|

|

Логические элементы на КМОП-структурах

КМОП – это сокращение от слов комплементарный, метал, окисел, проводник – означающих тот факт, что в одной и той же схеме присутствуют как n-канальные, так и р-канальные МОП-транзисторы. Все транзисторы нормально закрытые. КМОП-вентиль состоит из двух частей, одна из которых понижает потенциал на выходе при определенных условиях на входе, а другая, наоборот, повышает уровень выходного сигнала при других сигналах на входе. Обе части выполнены в виде схем с непосредственной связью.

Рис.4.13. КМОП-инвертор

В рамках положительной логики при логической «1» на входе инвертора нижний транзистор обеспечивает логический «0» на выходе (так как он открыт), а при логическом нуле на входе верхний транзистор повышает уровень на выходе до логической «1» (так как верхний транзистор открыт, а нижний – закрыт).

Рис. 4.14. КМОП-вентиль И-НЕ с двумя входами

Основные отличия: 1. КМОП-логика обладает несколько более сложной структурой, чем n-МОП и р-МОП, и поэтому на ее основе нельзя достичь столь же высокой плотности. Однако в статике эта логика очень мало потребляет энергии. Это свойство очень важно для тех применений, когда питание поступает от батарей. 2. Коэффициент разветвления по выходу у КМОП-вентилей такой же большой, как и у n-МОП и р-МОП вентилей. 3. Быстродействие из-за емкостей между С-И-З в МОП-транзисторе ниже, чем у ТТЛ 4. КМОП-вентили могут работать в широком диапазоне питающего напряжения. В частности, Uпитания может иметь любое значение в пределах от 3 до 15 В, благодаря этому КМОП логику можно совмещать с ТТЛ выбрав Uпитания = + 5 В. В этом случае КМОП-вентиль может управлять двумя входами ТТЛ.

Типовые логические узлы Триггеры

Триггер – это последовательностная схема с двумя состояниями, каждое из которых при определенных условиях на входах поддерживается постоянным. Когда на выходной линии триггера логическая «1», говорят, что триггер установлен. В противном случае говорят, что триггер сброшен.

Триггер типа RS

RS-триггер имеет два входа S (set – устанавливать) и R (recet – сбросить).

Таблица 5.1 – Таблица состояний RS-триггера

Рис.5.1. Построение простого RS-триггера на базе элемента стрелка Пирса (а) и штрих Шеффера (б)

Достоинство простого RS-триггера – минимальное количество элементов. Недостаток – любое случайное изменение сигналов на входах приводит к ложным срабатываниям триггера. Синхронный триггер

В синхронных системах хранящаяся в триггерах информация должна изменяться только в строго определенные моменты времени. Для этой цели в триггер вводится дополнительный вход, называемый входом синхронизации.

Рис.5.2. Синхронный RS-триггер

При нулевом значении синхроимпульса состояние триггера фиксировано и не реагирует на изменения входных сигналов. При «1» вентили 1 и 2 открыты и состояния входов S, R в соответствии с таблицей 5.1 определяют состояние выхода синхронного триггера.

Двухтактный RS-триггер (МS-триггер)

Двухтактный RS-триггер обеспечивает одновременную запись новой информации в триггер и считывание предыдущей.

Рис.5.3. Двухтактный RS-триггер.

С помощью инвертора (3) осуществляется двухфазное управление RS-триггерами (1) и (2). при С = 1 в триггер (1) записывается новая информация, при этом триггер (2) по входу С закрыт и продолжает хранить предыдущую информацию. При С = 0 триггер (1) перестает реагировать на состояние входов R и S. В то же время для триггера (2) С = 1 и выход триггера (1) переписывается в триггер (2) то есть на выход двухтактного триггера.

D-триггер

D-триггер обеспечивает запись сигналов «0» или «1» по одному входу при наличии синхроимпульса по входу С.

Рис.5.4. Однотактный D-триггер D-триггер аналогично RS-триггерам может быть однотактным и двухтактным.

Т-триггер (счетный триггер)

Счетный триггер обеспечивает последовательное деление количества поступающих на счетный вход импульсов на 2.

Рис.5.5. Т-триггер

JK-триггер

JK-триггер представляет собой обобщенную версию RS-триггера. Вход J соответствует входу S, а вход K соответствует входу R. Разница в поведении триггеров RS и JK обнаруживается, когда на оба JK входа подается логическая «1». В то время как поведение RS-триггера для входной комбинации R = 1, S = 1 не определено, поведение JK-триггера аналогично поведению Т-триггера. То есть по синхроимпульсу JK-триггер изменяет свое состояние на противоположное.

Рис.5.6. JK-триггер

Триггеры, переключаемые фронтом синхроимпульсов

Одно из свойств двухтактного D-триггера (рис.5.7.) состоит в том, что как опрос входных сигналов, так и обновление выходных происходит по фронту (в нашем случае отрицательному) синхроимпульса. Для этого типа триггера состояние ведущей секции реагирует на изменение входного сигнала все время, пока синхроимпульс имеет значение «1». То значение, которое будет иметь вход D непосредственно перед отрицательным фронтом синхроимпульса, определит окончательное состояние ведущей секции. Именно это состояние будет передано ведомой секции сразу после отрицательного фронта синхроимпульса. Следовательно, входной сигнал должен иметь правильное значение только в течении небольшого отрезка времени (равного времени срабатывания ведущей секции) непосредственно перед отрицательным фронтом синхроимпульса.

Рис.5.7. Двухтактный D-триггер, переключаемый фронтом импульса

О триггерах, обладающих таким свойством, говорят как о триггерах, переключаемых фронтом синхроимпульса. Ранее описанные триггера RS (рис.5.3.), JK (рис.5.6.) и T (рис.5.5.) не обладают этим свойством, поскольку окончательное состояние ведущей секции зависит от значения входного сигнала на всем интервале времени, когда синхроимпульс равен «1». Так для RS-триггера окончательное состояние ведущей секции зависит от того, какой из входов R или S, последним принимал значение «1» за время синхроимпульса.

Асинхронные входы в триггерах

Среди триггеров широко распространены триггеры с дополнительными входами, функции которых не зависят от сигналов синхронизации. Часто добавляются два входа, «предустановка» и «очистка», с помощью которых триггер может быть установлен в нужное состояние независимо от сигналов на других входах, включая синхронизирующий. Поскольку эти входы работают независимо от синхронизации, их называют асинхронными.

Рис.5.8. RS-триггер с асинхронными входами

Регистры Регистром называется устройство, предназначенное для записи и хранения одного дискретного «слова» - двоичного числа или иной кодовой комбинации. Помимо хранения записанной информации с помощью регистра можно получить инвертированный код «слова», осуществлять сдвиг информации на один или несколько разрядов, последовательный код преобразовывать в параллельный и наоборот. Основными элементами регистра являются триггеры. Число триггеров определяется числом двоичных разрядов «слова». По принципу работы регистры разделяются на регистры без сдвига и регистры со сдвигом (сдвигающие регистры). Последние в свою очередь могут быть двухтактными и однотактными.

Регистр без сдвига (параллельный регистр)

При подаче (рис.5.9.) управляющего импульса на шину R все D-триггера регистра устанавливаются в положение «0» (регистр обнуляется). Ввод новой информации осуществляется через D-входы триггеров по сигналу запись, поступающему на вход С.

Рис.5.9. Параллельный восьмиразрядный регистр, построенный на D-триггерах

Регистры со сдвигом информации (последовательные регистры)

Сдвиги данных в регистре – одна из основных операций в цифровых системах. С ее помощью решаются такие задачи, как преобразование данных из последовательной в параллельную форму и обратно, умножение и деление на степени двойки, позиционирование данных, последовательное хранение данных. При каждом синхроимпульсе (рис.5.10.) все триггера, за исключением самого левого, будут принимать текущее состояние своего левого соседа. Состояние крайнего левого триггера определяется входом «последовательный вход» (D).

Рис.5.10. Последовательный регистр, построенный на двухтактных D-триггерах Последовательно-параллельные регистры

Рис.5.11.

Последовательно-параллельные регистры обеспечивают как сдвиг информации, так и предварительную запись и считывание информации со всех триггеров регистра.

Примеры регистров в интегральном исполнении

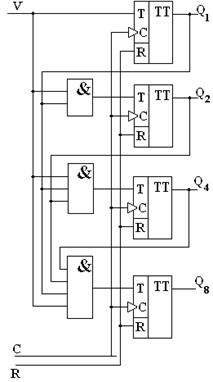

Рис.5.12. 8-разрядный последовательный сдвигающий регистр с параллельным входом (а) 4-разрядный универсальный сдвигающий регистр (б) Счетчики В общем виде счетчик – это последовательностная схема, в основе которой лежит регистр и которая в ответ на импульсы на специальной линии проходит через предписанную последовательность состояний. Счетчики с циклической повторяющейся последовательностью состояний называются счетчиками по модулю. Счетчики по модулю характеризуются как модулем, так и типом счетной последовательности, которая в частности, может быть двоичной, двоично-десятичной, в коде Грея и др.

Двоичные счетчики

Двоичный счетчик представляет собой совокупность Т-триггеров, каждый из которых ассоциируется с битом в двоичном представлении числа. Если в счетчике n триггеров, то число возможных состояний счетчика ровно 2n, и следовательно, его модуль также равен 2n. Счетная последовательность в двоичном суммирующем счетчике начинается с 0 и доходит до максимального числа 2n – 1, после чего снова проходит через 0 и повторяется. В вычитающем двоичном счетчике последовательные двоичные числа перебираются в обратном порядке, и максимальное число следует за 0 при повторении последовательности.

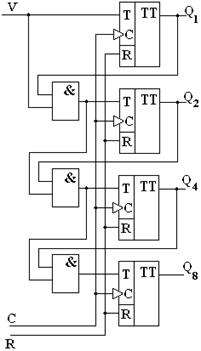

Рис.5.13. Асинхронный двоичный суммирующий счетчик

В счетчике (рис.5.13.) каждое изменение состояния левого триггера вызывает изменение состояния триггера справа. Другими словами, волна изменений состояния будет распространяться последовательно, асинхронно слева, направо. Для синхронных АУ нужно, чтобы все триггеры во всех компонентах изменяли свои состояния одновременно по синхроимпульсу. Поэтому асинхронные счетчики неприменимы в таких ситуациях.

Рис.5.14. Параллельный синхронный двоичный суммирующий счетчик.

Вычитающие счетчики

Вычитающие счетчики могут быть как синхронными, так и асинхронными. Построение вычитающих счетчиков аналогично суммирующим с той лишь разницей, что к последующему триггеру подключается не прямой, а инверсный выход предыдущего.

Рис.5.15. Синхронный вычитающий счетчик Если с помощью логических элементов организовать переключение выходов Q* или Q предыдущего триггера на вход последующего, то счетчик становится реверсивным и может, как суммировать, так и вычитать.

Принцип организации счетчика с модулем не являющемся степенью числа 2

Если для асинхронного входа установки в «0» (R), имеющегося в счетчике, сформировать с помощью логических элементов И цепь, в которой сигнал «1» будет появляться в зависимости от требуемой комбинации на выходе счетчика, то данный счетчик будет сбрасываться в «0» каждый раз, как только эта комбинация будет появляться, то есть счетчик будет делить не на 2n, а на меньшее число раз в зависимости от комбинации.

Рис. 5.16. двоичный четырехразрядный счетчик с коэффициентом деления 6.

Десятичные счетчики

Десятичный счетчик состоит из нескольких подсчетчиков, соответствующих десятичным разрядам. Подсчетчики считают по модулю 10, и их называют декадными счетчиками. Наиболее распространено представление в двоично-кодированном десятичном коде 8421, в котором каждая десятичная цифра кодируется четырехразрядным двоичным числом. Счетная последовательность суммирующего декадного счетчика в этом случае совпадает с двоичной последовательностью от 0000 до 1001, после чего следует снова 0. и последовательность повторяется.

а) б)

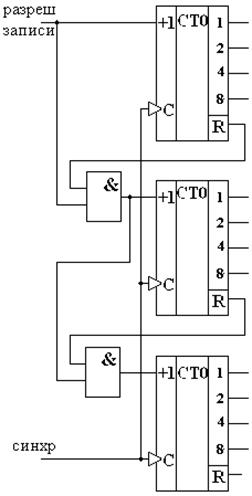

Рис.5.17.Принцип организации счетчика ст10 (а); трех декадный синхронный суммирующий счетчик, работающий в коде 8421 (б ).

Выход (Р) у каждого счетчика является выходом переноса (сигнал «1» на выходе Р появляется при числе в счетчике равном 9).

Кольцевые счетчики

В качестве счетчика может быть использован сдвигающий регистр, замкнутый в кольцо цепью обратной связи (рис.5.18.).

Рис.5.18. Кольцевой счетчик. D1-D4 – условное обозначение D-триггеров

В этом счетчике продвигается одна единица, которая при подаче очередного продвигающего импульса передается в следующую по порядку ячейку. Дойдя до конца регистра, единица записывается в первую ячейку и счет повторяется. Количество D-триггеров в счетчике должно быть равно необходимому числу состояний n = N или необходимому коэффициенту деления, если счетчик используется в качестве делителя. Очевидно, что при больших коэффициентах деления простейший кольцевой счетчик становится неэкономичным, так как требует столько же триггеров. Для уменьшения количества триггеров используется последовательное соединение кольцевых счетчиков. В этом варианте выходной сигнал одного кольцевого счетчика является продвигающим импульсом для другого.

Рис.5.19.

Коэффициент деления счетчика рис.5.19 равен N = n · m. При n ≈ m требуется минимальное количество D-триггеров при заданном N.

Примеры комбинационных схем Дешифраторы

Дешифратор основного типа, то есть дешифратор «1 из 2n», представляет собой комбинационную схему с n входами и 2nвыходами. Каждая выходная линия однозначно соответствует одной из 2n возможных комбинаций входных сигналов. Таблица 5.1.

Рис.5.20. Дешифратор на три входа

Вход V (разрешение) управляет всеми выходными сигналами. Если на линию V подать «0» то все выходы установятся в «0».

Селекторы

Функцию выбора данных от одного или нескольких источников выполняют устройства, изготавливаемые в виде модулей и называемые селекторами. Как правило, селектор – это комбинационная схема с одной выходной линией для данных, 2n входными линиями для данных и n управляющими линиями. Каждая из 2n входных линий соответствует одной из 2n возможных комбинаций сигналов на n входных управляющих линиях. При заданной комбинации на входных управляющих линиях значение соответствующей входной линии данных передается на выходную линию данных.

Рис.5.21. Селектор на 4 линии.

Шифраторы-кодопреобразователи

Шифратор – комбинационная схема, преобразовывающая входную комбинацию сигналов в эквивалентный двоичный код. Типичным примером шифратора может служить преобразователь 8421 двоично-десятичного кода в семи сегментный код. Этот преобразователь получает десятичную цифру в четырех битовом двоично-десятичном представлении и формирует значения на семи выходных линиях, которые используются для управления семью сегментами светового индикатора.

Таблица 5.2

Рис.5.22. Шифратор-преобразователь двоично-десятичного кода в семи сегментный

Вход х5 предназначен для быстрого коммутирования выходных сигналов (32 Гц) необходимого для индикаторов на жидких кристалах.

Сумматоры и вычитатели

Полный сумматор

Сумматор предназначен для поразрядного складывания двух двоичных чисел А = аn-1 · an-2 · · · a1 · a0 и В = bn-1 · bn-2 · · · b1 · b0. При сложении двоичных чисел значения цифр в каждом двоичном разряде должны быть сложены между собой и с переносом из предыдущего разряда. Если результат при этом превышает 1, то возникает перенос в следующий разряд. Полным сумматором называется сумматор суммирующий все три бита в разряде включая перенос. Составим таблицу состояний для суммирования ai + bi + ci

Таблица 5.2

Рис.5.24. Полный сумматор

Если покаскадно соединить n полных сумматоров то получается схема для сложения n разрядных двоичных чисел. Разряды складываемых чисел подаются на входы аi и bi, а результат появляется на выходах Si. Последний перенос Cn является старшим разрядом (n + 1) разрядной суммы. Входная линия переноса в младший разряд C0 является еще одним входом всей схемы. Он позволяет задать начальное значение переноса, что удобно для сложения с многократной точностью.

Рис.5.25. Двоичный сумматор с последовательным переносом

Полный вычитатель

Таблица 5.3

Заем в соседнем разряде считается отрицательным переносом. Таким образом разряд переноса Сi при вычитании может обозначать наличие заема из предыдущего разряда. Сравнивая таблицу 5.2 и таблицу 5.3 видим, что колонки Si идентичны. Следовательно, выражения для Si в вычитателе и сумматоре совпадают. Для Сi+1 выражения совпадают при условии замены аi* на аi, поэтому схема полного вычитателя аналогична схеме полного сумматора (рис.5.24.) с той лишь разницей, что для схемы формирования Сi+1 вместо сигнала аi взят сигнал аi*, то есть добавлен инвертор.

Генераторы прямоугольных импульсов

Рис.5.26.

Генераторы прямоугольных импульсов широко применяются в схемах синхронных УА для стробирования электронной части УА. Конденсатор С1 выбирается в зависимости от требуемой выходной длительности импульса. Схема формирования импульсов

a) Рис.5.27. Схемы формирователя (удвоителя) импульсов по фронту и срезу входного сигнала: а) на элементах НЕ, И, ИЛИ б) на элементе неравнозначность

б) Схема устранения дребезга контактов

Любой переключающийся контакт в момент переключения осуществляет кратковременные затухающие колебательные движения. При вводе в УА информации о положении датчиков двухпозиционной информации в схему УА поступает последовательность П импульсов обусловленных дребезгом контакта.

Рис.5.28. Схема наблюдения дребезга контактов при переключении

Последовательность импульсов дребезга может приводить к ложным управляющим воздействиям УА, если не предусматривать специальных мер устранения дребезга. Наиболее эффективным способом устранения дребезга является способ с использованием RS-триггера. В RS-триггере собранном на двух элементах И-НЕ при дребезге контактов (рис.5.29.) за счет резисторов R1, R2 поддерживается на входах S*, R* состояние логической «1», то есть состояние удержания, поэтому первым же импульсом логического «0» переключающегося контакта S1 триггер будет переброшен в противоположное состояние и будет удерживаться в нем при последующем дребезге.

Рис 5.29.Схема устранения дребезга контактов на RS-триггере |

|

Я

Я

1

1

1

1

1

1

1

1

1

1

1

1

1

1